#### High-Order Multi-Bit Delta-Sigma Modulator for Low OSR

Shahida Zeb, Arshad Hussain, Zeeshan Akbar Department of Electronics, Faculty of Natural Sciences Quaid-i-Azam University, Islamabad 45320-Pakistan <u>shahidazeb10@gmail.com</u>, <u>arshad@qau.edu.pk</u>

#### ABSTRACT

This paper presents a fourth-order multi-bit delta-sigma modulator to achieve higher performance for low oversampling ratio (OSR). The modulator topology considered cascade of resonator with multiple feedback structure (CRFB). The modulator employed the 4-bit guantizer with sixteen different levels. The signal transfer function (STF) and noise transfer function (NTF) discussed. The NTF zeroes are optimized to maximum suppression of quantization noise. Due to the feedback topology the STF of the CRFB structure shows flat rather than peaking for CRFF. It is observed the peak response in the STF for the case of CRFF is quite higher, as compared to the cascade of integrator with multiple feedforward topology. Also, the poles of the NTF lies insides the unit circle, while zeroes are spread on the DC in the unit circle in z-domain. It is also observed that the zeroes are at the origin and poles are spread close to DC in the unit circle for the case of STF. The multi-bit quantizer causes the quantization step smaller. The out-of-band gain (OBG) of the modulator is adjusted to 2.5 for maximum signal to noise ratio (SNR). The input signal amplitude for the higher order modulator is 0.55-V. The modulator is modeled in MATLAB and performance is evaluated for maximum SNR of 91 dB with OSR of 16. With OSR of 8, the modulator can achieve SNR of 62 dB.

Keywords: CRFB, CRFF, STF, Delta-Sigma Modulator, DC gain, unit circle

## 1. INTRODUCTION

A fourth order modulator design for low OSR to achieve wide bandwidth. The modulator can achieve SNR of 62 dB for low OSR of 8 and SNR of 51 dB for OSR of 6. The modulator can achieve SNR of 91 dB for OSR of 16. The modulator can achieve SNR of 117 dB with OSR of 32. A oversampling ADC is modeled and simulated for signal bandwidth of 20 MHz with OSR of 16 having sampling frequency of 640 MHz. The non-idealities like finite DC gain of operational amplifier and thermal noise of the complete modulator model also simulated. This paper presents a 2-2 discrete-time sturdy multistage noise-shaping (SMASH) delta-sigma modulator using source-follower-based open-loop integrators. The resolution of the SMASH delta-sigma modulator is

enhanced by eliminating the first-stage quantization noise from the output. Using the proposed source-follower-based open-loop integrator, the operating speed of the modulator is efficiently improved. The prototype delta-sigma modulator fabricated in a 65-nm CMOS process achieves a 75.8-dB dynamic range and 72.9-dB SNDR in a 20-MHz bandwidth. The modulator occupies an active area of mm<sup>2</sup>. 0.34 and its total power consumption is 20.4 mW from a 1.2-V supply voltage operating at a 500-MHz clock frequency [1]. A high-linearity Multi-stAge noise SHaping (MASH) 2-2-2 sigma-delta modulator (SDM) for 20-MHz signal bandwidth (BW) was presented. Multi-bit quantizers were employed in each stage to provide a sufficiently low guantization noise level and thus improve the signal-to-noise ratio (SNR)

performance of the modulator. Mismatch noise in the internal multi-bit digital-toanalog converters (DACs) was analyzed in detail, and an alternative randomization scheme based on multi-layer butterflytype network was proposed to suppress spurious tones in the output spectrum. Fabricated in a 0.18-µm single-poly 4-Complementary Metal Oxide metal Semiconductor (CMOS) process, the modulator occupied a chip area of 0.45mm<sup>2</sup>, and dissipated a power of 28.8mW from a 1.8-V power supply at a sampling rate of 320MHz. The measured spurious-free dynamic range (SFDR) was 94dB where 17-dB improvement was achieved by applying the randomizers for multi-bit DACs in the first two stages. The peak signal-to-noise and distortion ratio (SNDR) was 76.9dB at -1 dBFS @ 2.5-MHz input, and the figure-of-merit (FOM) was 126pJ/conv [2]. A 40 MHz-12-bit bandwidth (BW) delta-sigma modulator (DSM) fabricated in 90 nm CMOS is presented. А noise-free capacitive local feedback scheme is proposed for noise transfer function complex zeros generation. Moreover, the operational transconductance amplifiers (OTAs) are implemented with a currentsharing feedforward technique to largely reduce the power and to boost the gain. With a 960 MHz clock frequency and 1.2 V supply, the modulator achieves 74.4 dB dynamic range and 69.7 dB peak signalto-noise and distortion ratio (SNDR). The DSM FoM is 0.22 pJ/conv, which is among the lowest of the published moderate resolution DSMs in this high-bandwidth range [3]. A dual-mode second-order reconfigurable quadrature bandpass continuous-time delta-sigma modulator is presented for a low-IF global navigation satellite system receiver to simplify the entire architecture. The proposed modulator is capable of supporting both narrowband of 5-MHz bandwidth (BW) and wideband of 20-MHz BW. An amplifier topology with active feedforward and antipole-splitting compensation schemes is proposed. The flexible amplifiers in active-RC integrators and preamplifiers in implemented comparators are with power scaling technique to effectively adjust the power consumption for both BWs. A 1-bit digitally switched current digital-toanalog converter structure with gate-leakage compensation and lowlatency dynamic element matching is proposed to cover large current variations and mitigate the gate-leakage Digital self-calibration issue. I/Q algorithm is realized to improve the image rejection ratio (IRR). Implemented in 65-nm CMOS, the  $\Delta\Sigma$  modulator achieves 67.8-/61.4-dB dynamic range, 65.9-/53.7-dB signal-to-noise-plusdistortion ratio, and >60-dB IRR after calibration across 5-/20-MHz BW with center frequencies of 4/12 MHz. respectively. Powered by a 1.2 V supply, the modulator only consumes 4.2/8.1 mW, resulting in measured figure-ofmerits of 0.26/0.51 pJ/conversion step [4]. A third-order continuous-time Delta-Sigma modulator in a 130 nm CMOS technology is presented. It features a 3bit guantizer with an intrinsic excess loop delay compensation for half a clock cycle. The compensation is performed by means of adapting the reference voltages of the comparators on a sampling-tosampling base, thus overcoming a power consuming summation of signals in front of the quantizer. Occupying merely 0.086mm 2, the modulator achieves 66.4 dB SNDR and 74.6 dB DR in a 20 MHz bandwidth using a 640 MHz clock frequency. The power consumption equals 5.1 mW drawn from a 1.2 V supply voltage, which yields a state-of-the-art Walden figure of merit FOM W of 74.7 fJ/conv-step [5].

This paper proposed a fourth-order multibit delta-sigma modulator to achieve higher performance for low oversampling ratio (OSR). The modulator topology considered cascade of resonator with multiple feedback structure (CRFB). The modulator employed the 4-bit quantizer with sixteen different levels. The signal transfer function (STF) and noise transfer function (NTF) discussed. The NTF zeroes are optimized to maximum suppression of guantization noise. Due to the feedback topology the STF of the CRFB structure shows flat rather than peaking for CRFF. It is observed the peak response in the STF for the case of CRFF is quite higher, as compared to the cascade of integrator with multiple feedforward topology. Also, the poles of the NTF lies insides the unit circle, while zeroes are spread on the DC in the unit circle in z-domain. It is also observed that the zeroes are at the origin and poles are spread close to DC in the unit circle for the case of STF. The multibit quantizer causes the quantization step smaller. The out-of-band gain (OBG) of the modulator is adjusted to 2.5 for maximum signal to noise ratio (SNR). The input signal amplitude for the higher order modulator is 0.55-V. The modulator is modeled in MATLAB and performance is evaluated for maximum SNR of 91 dB with OSR of 16. With OSR of 8, the modulator can achieve SNR of 62 dB. NTF zero optimization techniques shifts these zeroes at the DC and suppress the quantization noise in the signal band.

introduction, After the the second section discuss the design of the modulator design with CIFB structure, while the third section describes the modeling and simulation of the modulator and explain the operational amplifier for integrator for the fifthorder 4-bit quantizer for design implementation. Finally, the section four concludes the paper.

#### 2. MODULATOR DESIGN

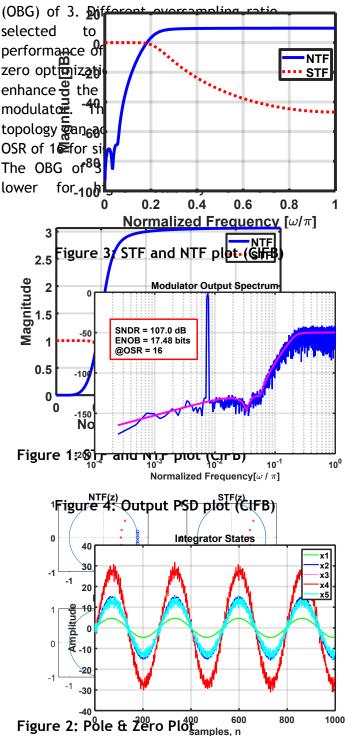

A higher order modulator with five integrators inside the loopfilter and fourbit quantizer modeled using Delta-Sigma Toolbox [12]. The cascade of integrator with multiple feedforward (CIFB) topology employed to investigate the performance for higher out-of-band-gain

Figure 5: Output states of the integrators

modulator as shown in the Figure 1. The STF, NTF poles and zeroes plots are shown in the Figure 2. All NTF zeroes optimized after NTF shows zero optimization techniques employed. Due to the reason of low pass modulator, the STF of the modulator have low pass behavior. While the NTF have high pass response to shape more guantization noise at high frequency. The signaltransfer function (STF) and noise transfer function (NTF) of the modulator is shown in Figure 3. As it is shown from the Figure 1 clearly that the OBG of the CIFB modulator is 3. While STF of the modulator shows low-pass response to allow those signals, which are at low frequencies and attenuate high frequency signal. The Figure 4 shows the output power spectral density (PSD) plot with SNR of 107, achieving effective number of bit (ENOB) of 17-bit. The modulator NTF shows a sharp noise shaping response due to the reason that all integrator inside the loopfilter is assumed having infinite DC gain. The noise floor is at the level of -145dB, the guantization noise is suppressed maximum with nine integrators inside the loop filter. Due to moderate OSR of 16, the signal bandwidth is 20 MHz. Figure 5 shows that the due to CIFB topology of the modulator the signal swing inside the loopfilter is large as a results operational amplifier with very high DC gain will be demanded for the suppression of the quantization noise. Due to CIFB topology the stability of the loopfilter is very high due to the advantage of multiple feedbacks, while the overall modulator becomes power hungry with many high DC gain amplifier inside the loopfilter.

## 1. RESULTS & DICUSSION

An oversampling ADC for signal bandwidth of 20 MHz. The loop filter implements CIFB topology the in MATLAB. The modulator can achieve SNR of 107 dB with NTF zero optimization technique. The simulation environment SDToolbox [14] which simulates the circuit nonidealities are used. This section will discuss about the circuit non-idealities like thermal noise or kT/C, flicker noise, finite operational amplifier gain, finite slew-rate, finite gain-bandwidth (GBW).

## 4. CONCLUSION

А fourth-order multi-bit delta-sigma modulator to achieve higher performance for low oversampling ratio (OSR). The modulator topology considered cascade of resonator with multiple feedback (CRFB). The structure modulator employed the 4-bit quantizer with sixteen different levels. The signal transfer function (STF) and noise transfer function (NTF) discussed. The NTF zeroes are optimized to maximum suppression of quantization noise. Due to the feedback topology the STF of the CRFB structure shows flat rather than peaking for CRFF. It is observed the peak response in the STF for the case of CRFF is guite higher, as compared to the cascade of integrator with multiple feedforward topology. Also, the poles of the NTF lies insides the unit circle, while zeroes are spread on the DC in the unit circle in z-domain. It is also observed that the zeroes are at the origin and poles are spread close to DC in the unit circle for the case of STF. The multibit quantizer causes the quantization step smaller. The out-of-band gain (OBG) of the modulator is adjusted to 2.5 for maximum signal to noise ratio (SNR). The input signal amplitude for the higher order modulator is 0.55-V. The modulator is modeled in MATLAB and performance is evaluated for maximum SNR of 91 dB

with OSR of 16. With OSR of 8, the modulator can achieve SNR of 62 dB.

# 5. ACKNOWLEDGMENT

This research work was supported by System-on-Chip Design Laboratory (SoC), Department of Electronics, Faculty of Natural Sciences, Quaid-i-Azam University, Islamabad, Pakistan.

## 6. **REFERENCES**

- [1] Y. Kwak, et al, 2017, A 72.9-dB SNDR 20-MHz BW 2-2 discretetime sturdy MASH delta-sigma modulator using source-follower based integrators, IEEE Asian Solid-State Circuit Conference, Nov 6-8, 2017.

- [2] D. Li, et al, 2020, A 20-MHz MASH Sigma-Delta Modulator with Mismatch Noise Randomization, Journal of circuit, system and computers, 29(7), pp. 1846-1855.

- [3] X. Xing, et al,2013, A 40MHz BW Continuou-time delta-sigma modulator with capacitive local feedback and currebr sharing OTA IET, 49(9).

- [4] Y. Xu, et al, 2015, A 5-/20-MHz BW Reconfigurable Quadrature Bandpass CT  $\Delta\Sigma$  ADC With AntiPole-Splitting Opamp and Digital I / Q Calibration, IEEE Trans on VLSI: Regular paper, 24(1), pp. 243-255.

- [5] C. Ding, et al, 2015, A 5.1mW 74dB DR CT ΔΣ modulator with quantizer intrinsic ELD compensation achieving 75fJ/conv.-step in a 20MHz , IEEE ESSCIRC Conference.

- [6] Yoon D, et al, 2015, A continuous-time sturdy-MASH Delta-Sigma Modulator in 28nm CMOS, IEEE Journal of Solid-State Circuit, 50(12), pp. 2880-2890.

- [7] S. Norsworthy, Richard Schreier, G.C. Temes, 1997,

Delta-Sigma Data Converter Theory, Design, and Simulation, John Wiley & Sons, Inc., Hoboken, New Jersey.

- [8] Yao Xiao, et al, 2020, A 100-MHz Bandwidth 80-dB Dynamic Range Countinuous-time Delta-Sigma Modulator with a 2.4-GHz Clock Rate, Nanoscale Research Letters.

- [9] Wei Wang, at al., 2019, A 72.6dB SNDR 100MHz BW 16.36mW CTDSM with Preliminary Sampling and Quantization Scheme in Backend Subranging QTZ, IEEE Internation Conference of Solid-State Circuit & Conference (ISSCC), pp. 340-342.

- [10] Sheng-Jui Huang, et al., 2017, A 125MHz-BW 71.9dB-SNDR VCO-Based CT delta-sigma ADC with segmented Phase-Domain ELD Compensation in 16nm, IEEE International Solid-State Circuit Conference (ISSCC), pp. 470-472.

- [11] Yunzhi Dong , et al., 2016, A 930mW 69db-DR 465MHz-BW CT 1-2 MASH ADC in 28 nm CMOS, IEEE International Solid-State Circuit Conference (ISSCC), pp. 278-280.

- [12] R. Scherier Delta-Sigma Toolbox ((<u>http://www.mathworks.com/m</u> <u>atlancentral/fileexchange/19-</u> <u>delta-sigma-toolbox</u>).

- [13] Shanti Paven, Richjard Schreier and G.C. Temes, Understanding Delta-Sigma Data Converters Second Edition, IEEE Press Wiley

- [14] S. Brigati SDToolbox (http://www.mathworks.com/ma tlabcentral/fileexchange/2460-sdtoolbox).